# A PVT Aware Accurate Statistical Logic Library for High- $\kappa$ Metal-Gate Nano-CMOS

Dhruva Ghai<sup>1</sup>, Saraju P. Mohanty<sup>1</sup>, Elias Kougianos<sup>1</sup>, Priyadarsan Patra<sup>2</sup>

<sup>1</sup> VLSI Design and CAD Laboratory (VDCL), University of North Texas, Denton, TX 76203, USA.

<sup>2</sup> Validation Research Lab, Intel Corporation, Hillsboro, OR 97124, USA.

<sup>1</sup> Email-ID: saraju.mohanty@unt.edu

#### **Abstract**

The semiconductor industry is headed towards a new era of scaling and uncertainty with new key building blocks for the next-generation chips, the high- $\kappa$  metal-gate transistor. There is a need for statistical characterization of high- $\kappa$  metal-gate digital gates as a function of process parameter variations to make them available for designers. In this paper, we present a methodology for PVT aware high- $\kappa$  metal-gate logic library creation while considering the variability effect in 15 parameters. First, statistical models for GIDL current ( $\hat{I}_{GIDL}$ ), offcurrent  $(\hat{I}_{OFF})$  and drive current  $(\hat{I}_{ON})$  are presented at the device level. This is followed by statistical characterization of logic cells at room temperature. Data for subthreshold current  $(\hat{I}_{sub}), \hat{I}_{GIDL}$ , dynamic current  $(\hat{I}_{dyn})$  and delay is presented. This is followed by results for PVT aware characterization of logic cells. To the best of the authors' knowledge, this is the first research which provides a PVT aware statistical characterization for high- $\kappa$  metal-gate nano-CMOS based logic gates.

#### Keywords

Nanoscale CMOS, High- $\kappa$  metal-gate technology, Monte Carlo, Gate Induced Drain Leakage (GIDL), Subthreshold Leakage, Dynamic Power

#### 1 Introduction and Contributions

The success of the semiconductor industry relies on the continuous improvement of integrated circuit performance which is achieved by device scaling. The superior properties of  $\mathrm{SiO}_2$  allow the fabrication of properly working devices with  $\mathrm{SiO}_2$  layers as thin as 1.5nm. However, further scaling of  $\mathrm{SiO}_2$  layer thickness leads to tunneling gate leakage [2, 14]. The solution to this problem is to use a gate insulator with a higher dielectric constant  $\kappa$  than that of  $\mathrm{SiO}_2$  (= 3.9) and metal gate [9]. This reduces the gate leakage and improves the reliability of the gate. In this paper, we refer to this non-classical nano-CMOS structure as high- $\kappa$  metal-gate (HKMG) nano-CMOS. However, the use of HKMG causes a significant gate-induced drain leakage (GIDL) current ( $I_{GIDL}$ ) in addition to subthreshold leakage ( $I_{sub}$ ) [12].  $I_{GIDL}$  is high mainly due to two reasons:

- (1) The metal gate introduces a high gate effective work function which leads to high electric field and a high GIDL current [16].

- (2) The high- $\kappa$  gate dielectric and SiO<sub>2</sub> spacers meet at the surface of the drain region, causing a high electric field leading to a high GIDL current [8].

It is widely recognized that the uncontrollable statistical variability in device characteristics represents major challenges to scaling and integration for present and next generation nano-CMOS transistors and circuits. This in turn demands revolutionary changes in the way in which future integrated circuits and systems are designed. Strong links must be established between circuit design, system design and fundamental device technology to allow circuits and systems to accommodate the increasing variability. The major sources of variability are: process variation (P), supply voltage (V), and operating temperature (T) which may be due to the environment, through self-heating effects or a combination of the two.

Unfortunately, PVT variability makes it hard to achieve "safe" integrated circuit designs in nanometer technologies. This is because PVT variability causes fluctuation in timing as well as power for System-on-Chip (SoC) designs [7]. Till now very few efforts have been made at addressing the effect of PVT variability on power, leakage and delay estimation. It is necessary to express each of these factors as a function of process, voltage and temperature (PVT):

$$\hat{Y} = f(P, V, T), \tag{1}$$

where  $\hat{Y}$  is power, leakage or delay. Also, for nano-CMOS, a shift from deterministic to probabilistic design is required to accommodate the effects of device variability, which involves extensive use of statistical techniques. The challenges for such modeling are several:

- (1) There is a need for realistic evaluation of circuit delay and power variability, considering processes variation and correlations between them.

- (2) There is a need to directly relate variability in circuit parameters to variability in process parameters.

(3) There is a need to migrate from corner-based timing to statistical timing for accuracy.

To address these challenges, we propose a Monte Carlo based technique to create a PVT aware library, which has the following advantages:

- (1) Accurate estimation of power, leakage and delay in emerging non-classical CMOS structures is possible.

- (2) A closed form function relating the output to input is not required, which otherwise would have been cumbersome for the large number of parameters considered in this paper.

- (3) Parameters take on more realistic or practical extreme values resulting in densely designed, reliable, manufacturable circuits.

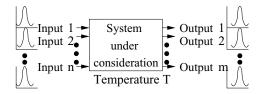

Figure 1. Logic level modeling for PVT aware statistical library.

Figure 1 shows the logic level modeling for a system under consideration for which a PVT aware library is to be created. The inputs to the system are probability density functions (PDFs) of the sources of variability. In this paper, the system under consideration is logic gates, as the goal is a logic library creation. The input PDFs are denoted as  $\hat{X}_j$ , where  $j=1 \rightarrow n$ . The logic gate is then subjected to Monte Carlo simulations. The output of the system are the PDFs for outputs as functions of the inputs, which are process parameters (P) and voltage (V), at a specific temperature (T). The output PDFs are denoted as  $\hat{Y}_i$ , where  $i=1 \rightarrow m$ . These simulations run for different temperatures and a PVT aware library is obtained.

#### The novel contributions of this paper are as follows:

- A methodology for HKMG logic library creation is presented.

- (2) The effect of process variations has been considered during logic library creation.

- (3) Device level characterization of HKMG NMOS and PMOS transistors is presented.

- (4) An HKMG logic library with statistical characterization at room temperature (27°C) is presented.

- (5) A PVT aware HKMG statistical logic library is presented.

The rest of the paper is organized as follows: Section 2 discusses related research. The proposed methodology for logic library creation is discussed in section 3 highlighting the various sources of variability. The power, leakage and delay models used in this paper are presented in section 4. Section 5 presents the statistical characterization of HKMG NMOS and PMOS devices. Section 6 presents the statistical characterization of the HKMG logic library at room temperature. PVT characterization results are presented in section 7. Section 8 discusses applications of the statistical logic library. The paper concludes in section 9.

#### 2 Related Prior Research

Logic libraries are required for fast design exploration. Statistical characterization of logic gates as a function of process and environment parameter variations is required [22, 14, 20]. To minimize power consumption and maximize timing performance, design teams require rapid library characterization and accurate modeling for specific operating conditions [18]. A large number of logic libraries are available in the market today for standard CMOS [3, 6]. However, as the industry moves away from classical CMOS, characterized standard cells for non-classical technologies will be required. This paper is a futuristic effort in this direction.

# 3 The Proposed Methodology For Logic Library

### 3.1 Sources of Variation and Nature of Variability

In this paper, we have considered 15 different parameters for variation. The parameters for variability are as follows: (1)  $V_{dd}$ : supply voltage (V), (2)  $V_{Thn}$ : NMOS threshold voltage (V), (3)  $V_{Thp}$ : PMOS threshold voltage (V), (4)  $t_{gaten}$ : NMOS gate dielectric thickness (nm), (5)  $t_{gatep}$ : PMOS gate dielectric thickness (nm), (6)  $L_{effn}$ : NMOS channel length (nm), (7)  $L_{effp}$ : PMOS channel length (nm), (8)  $W_{effn}$ : NMOS channel width (nm), (9)  $W_{effp}$ : PMOS channel width (nm), (10)  $N_{gaten}$ : NMOS gate doping concentration  $(cm^{-3})$ , (11)  $N_{qatep}$ : PMOS gate doping concentration  $(cm^{-3})$ , (12)  $N_{chn}$ : NMOS channel doping concentration ( $cm^{-3}$ ), (13)  $N_{chp}$ : PMOS channel doping concentration  $(cm^{-3})$ , (14)  $N_{sdn}$ : NMOS source/ drain doping concentration  $(cm^{-3})$ , (15)  $N_{sdp}$ : NMOS source/ drain doping concentration  $(cm^{-3})$ . These parameters are not necessarily independent. The statistical variability in most of these parameters can be modeled as Gaussian distributions [13].

### 3.2 Statistical Logic Library Characterization Flow

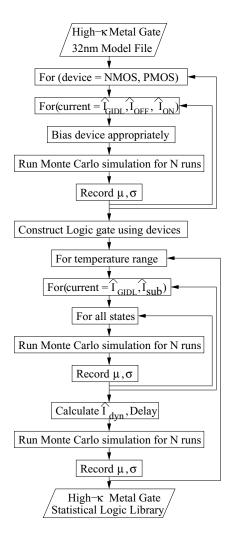

We present the proposed methodology followed in this paper for a PVT aware HKMG logic library creation, shown in figure 2. The input to the design flow is a 32nm HKMG model

Figure 2. The proposed methodology for PVT aware statistical logic library.

file. The first step in the flow involves the statistical characterization at device level i.e. NMOS and PMOS for  $\hat{I}_{GIDL}$ ,  $\hat{I}_{OFF}$  and  $\hat{I}_{ON}$ . For measurement of each current, the device has to be biased appropriately. The biasing conditions are discussed in detail in section 5. Monte Carlo simulations are run on the device to obtain statistical data (mean  $\mu$ , variance  $\sigma^2$ ) for each device. The second step in the flow involves PVT aware characterization of logic gates. At a given temperature, the logic gate under consideration is biased for each state and Monte Carlo simulations are performed to obtain the statistical data. We present state dependent data for  $\hat{I}_{GIDL}$  and  $\hat{I}_{sub}$ . This is followed by measurement of  $\hat{I}_{dyn}$  and delay.

#### 4 Power, Leakage, and Delay Models

#### 4.1 Gate Induced Drain Leakage (GIDL)

GIDL is caused by the existence of a high electric field at the drain junction of MOS transistors [8]. In NMOS transistors, GIDL takes place when the gate is at a lower potential than the

drain. This causes significant band bending in the drain, allowing electron-hole pair generation through avalanche multiplication and band to band tunneling. GIDL has a strong impact in HKMG transistors. Equation 2 shows the BSIM4 expression used for calculating GIDL [1]:

$$I_{GIDL} = A \times W_{effCJ} \times N_f \times \left(\frac{V_{ds} - V_{gs} - E}{3 \times T_{gate}}\right) \times \left(\frac{-3 \times T_{gate} \times B}{-V_{ds} - V_{qs} - E}\right) \times \left(\frac{V_{db}^3}{C + V_{db}^3}\right), (2)$$

where  $V_{db}$  is the drain to body voltage,  $V_{ds}$  is the drain to source voltage,  $V_{gs}$  is the effective gate voltage,  $W_{effCJ}$  is the effective width of the drain diffusions,  $N_f$  is the number of fingers of the transistor and A, B, C and E are all BSIM4 GIDL leakage-based parameters which have been fitted to existing data [16, 8, 12].

#### 4.2 Subthreshold Leakage

The subthreshold leakage through a CMOS device is modeled as follows [1, 17]:

$$I_{sub} = I_0 \times \left(1 - \exp\left(\frac{-V_{ds}}{v_{therm}}\right)\right) \times \exp\left(\frac{V_{gs} - V_{Th} - V_{off}}{S \times v_{therm}}\right), \tag{3}$$

where  $I_0$  is a constant dependent upon device parameters for a given technology,  $v_{therm}$  is the thermal voltage,  $V_{Th}$  is the threshold voltage,  $V_{off}$  is the offset voltage which determines the channel current at  $V_{gs}=0$ , S is the subthreshold swing factor,  $V_{gs}$  is gate-to-source voltage, and  $V_{ds}$  is the drain-to-source voltage.

In a nano-CMOS device, the threshold voltage  $V_{Th}$  is scaled along with the supply voltage in order to maintain performance. However, the systematic reduction in  $V_{Th}$  causes the subthreshold current to increase exponentially, as can be seen from equation 3.

#### 4.3 Dynamic Current

The dynamic power consumption of a circuit is expressed as follows [4]:

$$P_{dyn} = s \times C_L \times V_{dd}^2 \times f,\tag{4}$$

where the activity factor s captures how many devices are active on any particular clock cycle,  $C_L$  is the total switched capacitive load,  $V_{dd}$  is the supply voltage and f is the frequency of the clock. This power dissipation depends on loading condition and not the device features. The current associated with  $P_{dyn}$  is  $I_{dyn}$  and is calculated as the average of the current through the load capacitance  $C_L$ , given as:

$$I_{dyn} = \lim_{T \to \infty} \frac{1}{T} \int_{0}^{T} I_c(t) \times dt, \tag{5}$$

where  $I_c(t)$  is the current through the load capacitance  $C_L$ .

#### 4.4 Propagation Delay

The propagation delay  $(T_{PD})$  of a device is approximately calculated as follows [19]:

$$T_{PD} = \beta \times \left( \frac{C_L V_{dd}}{\mu \left( \frac{\kappa_{gate}}{T_{gate}} \right) \left( \frac{W_{eff}}{L_{eff}} \right) (V_{dd} - V_{Th})^{\alpha}} \right), \quad (6)$$

where  $\beta$  = a technology dependant constant ,  $\mu$  = electron surface mobility and  $\alpha$  is the velocity saturation index. The delay of logic cells is calculated as:

$$Delay = \left(\frac{T_{PDLH} + T_{PDHL}}{2}\right),\tag{7}$$

where,  $T_{PDLH}$  refers to the low to high transition, and  $T_{PDHL}$  refers to the high to low transition of the output.

#### 4.5 Method to Model high- $\kappa$ at Device Level

A 32nm Predictive Technology Model (PTM) available at [24] is used for modeling HKMG transistors. PTM provides a timely and effective analysis in the absence of published data and other device models. For high- $\kappa$  dielectric modeling using PTM, two methods are used: (1) The model parameter in the model card that denotes relative permittivity (EPSROX) is changed or (2) The equivalent oxide thickness (EOT) for the dielectric under consideration is calculated. The EOT is calculated by:

$$EOT = \left(\frac{\kappa_{SiO_2}}{\kappa_{gate}}\right) \times t_{gate},\tag{8}$$

where  $\kappa_{gate}$  is the relative permittivity and  $t_{gate}$  is the thickness of the gate dielectric material other than  $\mathrm{SiO}_2$ , while  $\kappa_{SiO_2}$  is the dielectric constant of  $\mathrm{SiO}_2$  (= 3.9). We have taken  $\kappa_{gate}=21$  and  $t_{gate}=5nm$  to emulate a HfO<sub>2</sub> based dielectric. EOT is calculated to be 0.9nm.

# 5 Variation Aware Device Level Characterization

Different biasing conditions have been used for device level characterization of the currents discussed in section 4. For reference, we have: (1) V(D) = voltage across drain, (2) V(G) = voltage across gate, (3) V(S) = voltage across source, (4) V(B) = voltage across bulk. For the NMOS device, for measuring  $I_{GIDL}$  and  $I_{OFF}$ , V(D) = 0.7V, V(G)= 0V, V(S) = 0V and V(B) = 0V. For measuring  $I_{ON}$ , V(D) = 0.7V, V(G)= 0.7V, V(G)= 0.7V, V(G)= 0.7V, V(G)= 0.7V and V(G)= 0.7V. For measuring  $I_{ON}$ , V(D)= 0.7V and V(G)= 0.7V and V(G)= 0.7V and V(G)= 0.7V and V(G)= 0.7V.

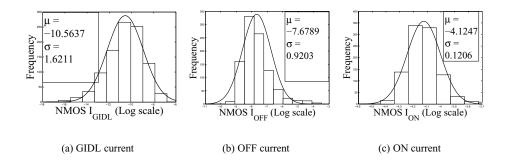

A Monte Carlo analysis with N =1000 runs has been run, with all the process parameters from section 3.1. Each of these process parameters is assumed to have a Gaussian distribution [10] with mean taken as the nominal values specified in the PTM [24] and standard deviation as 10% of the mean [21, 23].

$\hat{I}_{GIDL}$ ,  $\hat{I}_{OFF}$  and  $\hat{I}_{ON}$  exhibit lognormal distribution (figures 3(a), 3(b), and 3(c). Only the results for the NMOS transistors is shown. The PMOS data follow the same trends. The mean and standard deviation values for both transistor types are recorded in Table 1.

Table 1. Statistical data for HKMG devices

| Į | PDF of Cu        | rrents   | NMOS Device | PMOS Device |  |  |

|---|------------------|----------|-------------|-------------|--|--|

| ĺ | $\hat{I}_{GIDL}$ | $\mu$    | -10.5637    | -10.1050    |  |  |

| ı |                  | σ        | 1.6211      | 0.9927      |  |  |

| ĺ | $\hat{I}_{OFF}$  | $\mu$    | -7.6789     | -7.4682     |  |  |

| ı |                  | $\sigma$ | 0.9203      | 1.1446      |  |  |

| ĺ | $\hat{I}_{ON}$   | $\mu$    | -4.1247     | -4.1694     |  |  |

| ı |                  | σ        | 0.1206      | 0.1632      |  |  |

#### 6 Variation Aware State Dependent Logic Level Characterization

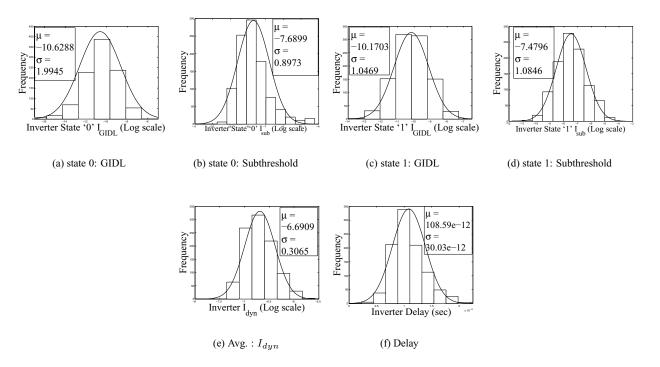

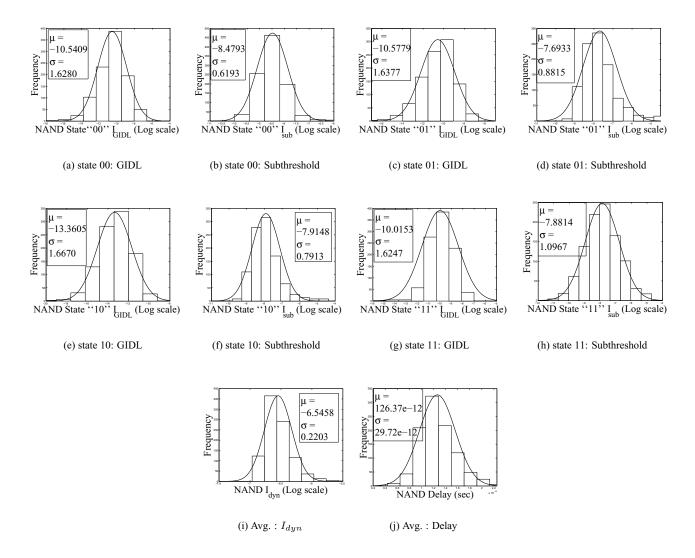

In this section we present the results for HKMG logic cells at room temperature  $(27^{\circ}C)$ . The results are presented for inverter and NAND gates for brevity. We present state dependent data for  $\hat{I}_{GIDL}$  and  $\hat{I}_{sub}$  as they lead to accurate leakage estimation. As  $I_{dyn}$  depends primarily on the switching of the logic gates, we present average data for  $\hat{I}_{dyn}$  as per equation 5.  $C_L$  is taken as 10 times  $C_{qq}$  (gate capacitance of PMOS).

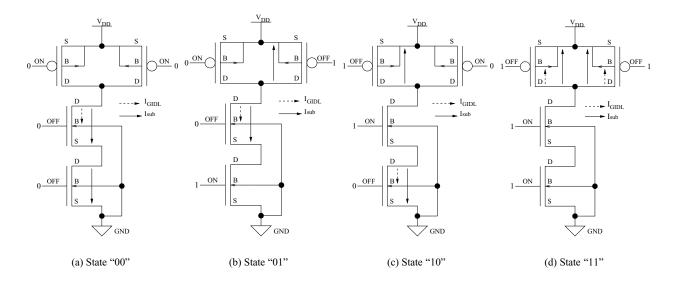

Tables 2 and 3 summarize the statistical data for the various currents measured in an inverter and a NAND gate. Results for only two gates are shown for brevity but the entire library is characterized following the same procedure. The direction of various currents in the NAND gate for each state are shown in figures 4(a), 4(b), 4(c), 4(d) and the distribution plots for these currents are shown in figures 5(a) to 6(j).

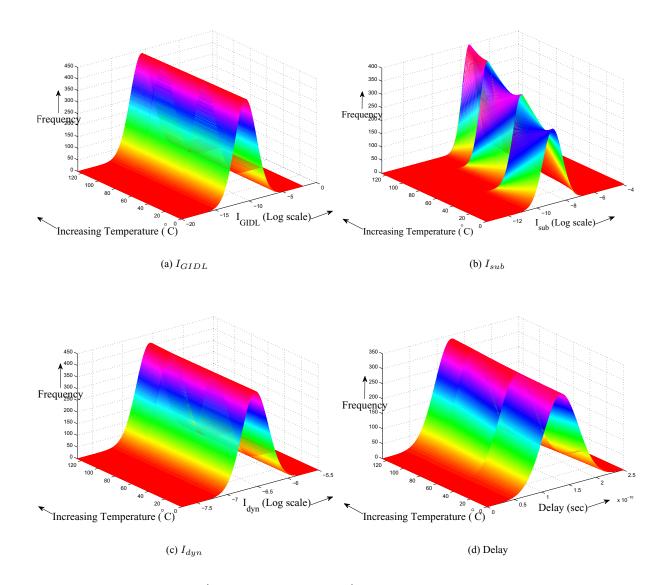

#### 7 PVT Aware Logic Level Characterization

This section presents the results for PVT aware logic library. Simulations at  $0^{\circ}\text{C}$ ,  $+50^{\circ}\text{C}$ ,  $+100^{\circ}\text{C}$ ,  $+125^{\circ}\text{C}$  are considered. It can be seen that  $\hat{I}_{GIDL}$  does not show strong dependence on temperature (figure 7(a)), while  $\hat{I}_{sub}$  shows an increase in the mean ( $\mu$ ) value with increasing temperature (figure 7(b)). This is due to dependence of  $\hat{I}_{sub}$  on  $V_{Th}$ , which depends strongly upon temperature. Delay also shows an increasing trend with temperature (figure 7(d).  $\hat{I}_{dyn}$  is measured over one cycle of operation, as per equation 5.  $\hat{I}_{dyn}$  remains almost constant with temperature, because for one cycle theoretically,  $\hat{I}_{dyn}$  does not depend on frequency [11]. The statistical results are summarized in Table 4. For brevity, the results for NAND gate are presented.  $\hat{I}_{GIDL}$  and  $\hat{I}_{sub}$  data are presented for state "00".

# 8 Applications For The Statistical Logic Library

Current circuit design methodologies, which depend on the existence of deterministic and uniform devices with no consid-

Figure 3. Distribution of  $\hat{I}_{GIDL}$ ,  $\hat{I}_{OFF}$ , and  $\hat{I}_{ON}$  for HKMG NMOS.

Figure 4. Flow of  $I_{sub}$  and  $I_{GIDL}$  for a high- $\kappa$  NAND gate for different states. The dotted line shows  $I_{GIDL}$  and the solid line represents  $I_{sub}$  flow.  $I_{GIDL}$  flows from drain to bulk, whereas  $I_{sub}$  flows from drain to source.

Table 2. Statistical state dependent data for an inverter.

| PDF of Cu        | rrents / Delay | '0' '1'             |          |  |  |

|------------------|----------------|---------------------|----------|--|--|

| $\hat{I}_{GIDL}$ | $\mu$          | -10.6288            | -10.1703 |  |  |

|                  | σ              | 1.9945              | 1.0469   |  |  |

| $\hat{I}_{sub}$  | $\mu$          | -7.6899             | -7.4796  |  |  |

|                  | σ              | 0.8973              | 1.0846   |  |  |

| $\hat{I}_{dyn}$  | $\mu$          | -6.6                |          |  |  |

|                  | $\sigma$       | 0.3                 |          |  |  |

| Delay            | $\mu$          | 108.59ps<br>30.03ps |          |  |  |

|                  | σ              |                     |          |  |  |

Table 3. Statistical state dependent data for a NAND.

| PDF of Cu        | rrents / Delay | "00"                | "01"     | "10"     | "11"                          |  |  |  |

|------------------|----------------|---------------------|----------|----------|-------------------------------|--|--|--|

| $\hat{I}_{GIDL}$ | $\mu$          | -10.5409            | -10.5779 | -13.3605 | -10.0153<br>1.6247<br>-7.8814 |  |  |  |

|                  | $\sigma$       | 1.6280              | 1.6377   | 1.6670   |                               |  |  |  |

| $\hat{I}_{sub}$  | $\mu$          | -8.4793             | -7.6933  | -7.9148  |                               |  |  |  |

|                  | $\sigma$       | 0.6193              | 0.8815   | 0.7913   | 1.0967                        |  |  |  |

| $\hat{I}_{dyn}$  | $\mu$          | -6.5458             |          |          |                               |  |  |  |

|                  | $\sigma$       | 0.2203              |          |          |                               |  |  |  |

| Delay            | $\mu$          | 126.37ps<br>29.72ps |          |          |                               |  |  |  |

|                  | σ              |                     |          |          |                               |  |  |  |

eration for either power consumption or probabilistic behavior, will no longer be sufficient to design robust circuits. This paper provides statistical state dependent characterization data for logic cells. The issue of providing characterization data for systems built using these logic cells is not in the scope of this paper. However, the data provided in this paper will be

useful at the system level when a probabilistic analysis is carried out. In [15], the authors characterize datapath components using a structural HDL. The data presented in this paper can also be useful for probabilistic-CMOS [5] where the analysis is done using probability distribution functions (PDFs), instead of working with actual values.

Figure 5. Distributions of GIDL ( $\hat{I}_{GIDL}$ ), subthreshold ( $\hat{I}_{sub}$ ), and dynamic ( $\hat{I}_{dyn}$ ) current, and delay for HKMG an inverter.

Table 4. PVT aware statistical data for HKMG a NAND logic cell.

| Temp  | Temp PDF of $\hat{I}_{GIDL}$ |        | PDF of $\hat{I}_{sub}$ |         | PDF of $\hat{I}_{dyn}$ |                        | PDF of Delay |        |                        |               |              |                        |

|-------|------------------------------|--------|------------------------|---------|------------------------|------------------------|--------------|--------|------------------------|---------------|--------------|------------------------|

| (° C) | $\mu$                        | σ      | $\frac{\sigma}{\mu}$ % | $\mu$   | σ                      | $\frac{\sigma}{\mu}$ % | $\mu$        | σ      | $\frac{\sigma}{\mu}$ % | μ             | σ            | $\frac{\sigma}{\mu}$ % |

| 0     | -10.5398                     | 1.6230 | 15.4                   | -8.9032 | 0.6763                 | 7.6                    | -6.5504      | 0.2184 | 3.3                    | $126.41 \ ps$ | 29.61 ps     | 23.42                  |

| 50    | -10.5418                     | 1.6325 | 15.5                   | -8.1738 | 0.5784                 | 7.1                    | -6.5442      | 0.2210 | 3.4                    | $127.19 \ ps$ | $30.12 \ ps$ | 23.68                  |

| 100   | -10.5443                     | 1.6432 | 15.6                   | -7.6394 | 0.5070                 | 6.6                    | -6.5441      | 0.2205 | 3.4                    | $131.55 \ ps$ | $31.52 \ ps$ | 23.96                  |

| 125   | -10.5457                     | 1.6490 | 15.6                   | -7.4228 | 0.4781                 | 6.4                    | -6.5439      | 0.2197 | 3.4                    | 134.8 $ps$    | 32.32~ps     | 23.98                  |

### 9 Conclusions and Future Directions of This Research

We have presented a methodology for a PVT aware HKMG standard cell library creation while considering the effect of process variations, in this paper. Device level characterization for HKMG NMOS and PMOS transistors for drive current  $(\hat{I}_{ON})$ , off-current  $(\hat{I}_{OFF})$  and GIDL current  $(\hat{I}_{GIDL})$  has been done, modeled using 32nm PTM models. This is followed by PVT aware statistical characterization of standard cells. The state dependent data for  $\hat{I}_{sub}$ ,  $\hat{I}_{GIDL}$  and dynamic current  $(\hat{I}_{dyn})$  are presented. As part of future work, we plan to implement similar logic libraries for other non-classical CMOS technologies such as double gate FET and Carbon Nanotubes and analyze their performance.

#### 10 Acknowledgments

This research is supported in part by NSF award number 0702361.

#### References

- [1] C. Hu, A. Niknejad, X. Xi, W. Liu, X. Jin, K. M. Cao, M. Dunga, and J. Ou. (2005, Jul. 29). BSIM4 MOS Models, Release 4.5.0. [Online]. http://www.device.eecs.berkeley.edu/~bsim3/bsim4.html.

- [2] Semiconductor Industry Association, International Technology Roadmap for Semiconductors. http://public.itrs. net.

- [3] Si2 Releases Open 45nm Library. https://www.si2.org/openeda.si2.org/projects/nangatelib.

- [4] S. S. A. Chandrakasan and R. W. Brodersen. Low Power CMOS Digital Design. *IEEE Journal of Solid-State Circuits*, 27(4):473–484, April 1992.

- [5] B. E. S. Akgul, L. N. Chakrapani, P. Korkmaz, and K. V. Palem. Probabilistic CMOS Technology: A Survey and Future Directions. In *Proceedings of the IFIP International Conference on Very Large Scale Integration*, pages 1–6, 2006.

- [6] S. Basu, P. Thakore, and R. Vemuri. Process Variation Tolerant Standard Cell Library Development Using Reduced Dimension Statistical Modeling and Optimization Techniques. In *Proceedings of the International Symposium on Quality Electronic Design*, pages 814–820, 2008.

Figure 6. Distributions of GIDL ( $\hat{I}_{GIDL}$ ), subthreshold ( $\hat{I}_{sub}$ ), and dynamic ( $\hat{I}_{dyn}$ ) current, and delay for a HKMG NAND.

- [7] S. Borkar, T. Karnik, and V. De. Design and reliability challenges in nanometer technologies. In *Proceedings of the Design Automation Conference*, pages 75–75, 2004.

- [8] S. Chang and H.Shin. Off-state leakage currents of mosfets with high- $\kappa$  dielectrics. *Journal of the Korean Physical Society*, 41(6):932–936, December 2002.

- [9] R. Chau, S.Datta, M. Doczy, J. Kavalieros, and M. Metz. Gate Dielectric Scaling for High-Performance CMOS: From SiO2 to High-κ. In *Proceedings of the International Workshop on Gate Insulator*, pages 124–126, 2003.

- [10] J. A. Croon, W. Sansen, and H. E. Maes. *Matching Properties of Deep Sub-Micron Transistors*. Springer, 2005.

- [11] A. Golda and A. Kos. Temperature influence on power consumption and time delay. In *Proceedings of the Euromicro Symposium on Digital System Design*, pages 378–382, 2003.

- [12] T. Lim and Y. Kim. Effect of band-to-band tunnelling leakage on 28 nm mosfet design. *IEE Electronic Letters*, 44(2):157– 158, January 2008.

- [13] T. Mizuno, J. Okamura, and A. Toriumi. Experimental study of threshold voltage fluctuation due to statistical variation of chan-

- nel dopant number in mosfet's. *IEEE Transactions on Electron Devices*, 41(11):2216–2221, November 1994.

- [14] S. P. Mohanty and E. Kougianos. Steady and Transient State Analysis of Gate Leakage Current in Nanoscale CMOS Logic Gates. In *Proceedings of the International Conference on Computer Design*, pages 210–215, 2006.

- [15] S. P. Mohanty, E. Kougianos, and D. K. Pradhan. Simultaneous scheduling and binding for low gate leakage nano-cmos datapath circuit behavioral synthesis. *IET Computers and Digital Techniques*, 2(2):118–131, March 2008.

- [16] S. G. Narendra and A. Chandrakasan. Leakage in Nanometer CMOS technologies. Springer, 2005.

- [17] A. Rastogi, K. Ganeshpure, and S. Kundu. A Study on Impact of Leakage Current on Dynamic Power. In *Proceedings of the International Symposium on Circuits and Systems*, pages 1069– 1072, 2007.

- [18] A. Rastogi, K. Ganeshpure, A. Sanyal, and S. Kundu. On composite leakage current maximization. *Journal of Electronic Testing: Theory and Applications*, 24(4):405–420, August 2008.

Figure 7. PVT plots for GIDL ( $\hat{I}_{GIDL}$ ), subthreshold ( $\hat{I}_{sub}$ ), and dynamic ( $I_{dyn}$ ) current, and delay for a HKMG NAND.

- [19] F. Sill, J. You, and D. Timmerman. Design of Mixed Gates for Leakage Reduction. In *Proceedings of the 17th Great Lakes Symposium on VLSI*, pages 263–268, 2007.

- [20] J. Singh, J. Mathew, S. P. Mohanty, and D. K. Pradhan. Statistical Analysis of Steady State Leakage Currents in Nano-CMOS Devices. In *Proceedings of the IEEE Norchip conference*, pages 1–4, 2007.

- [21] H. C. Srinivasaiah and N. Bhat. Response surface modeling of 100 nm CMOS process technology using design of experiment. In *Proceedings of the International Conference on VLSI Design*, pages 285–290, 2004.

- [22] S. Sundareswaran, J. A. Abraham, and A. Ardelea. Characterization of Standard Cells for Intra-Cell Mismatch Variations. In *Proceedings of the International Symposium on Quality Electronic Design*, pages 213–219, 2008.

- [23] L. Zhang, Z. Yu, and X. He. A Statistical Characterization of CMOS Process Fluctuations in Subthreshold Current Mir-

- rors. In *Proceedings of the International Conference on Quality Electronic Design*, pages 152–155, 2008.

- [24] W. Zhao and Y. Cao. New Generation of Predictive Technology Model for sub-45nm Design Exploration. In Proceedings of the International Symposium on Quality Electronic Design, pages 585–590, 2006.